PATENT 8023-1001

### IN THE U.S. PATENT AND TRADEMARK OFFICE

Applicant:

Ryosuke KOSAKA

Conf.:

Appl. No.:

NEW

Group:

Filed:

February 4, 2002

Examiner:

For:

SIGNAL LINE DRIVING CIRCUIT AND

SIGNAL LINE DRIVING METHOD FOR LIQUID

CRYSTAL DISPLAY

## CLAIM TO PRIORITY

Assistant Commissioner for Patents Washington, DC 20231

February 4, 2002

Sir:

TWP/ia

Applicant(s) herewith claim(s) the benefit of the priority filing date of the following application(s) for the above-entitled U.S. application under the provisions of 35 U.S.C. § 119 and 37 C.F.R. § 1.55:

Country

Application No.

Filed

JAPAN

2001-027042

February 2, 2001

Certified copy(ies) of the above-noted application(s) is(are) attached hereto.

Respectfully submitted,

YOUNG & PROMPSON

Reg. No. 33,027

745 South 23<sup>rd</sup> Street Arlington, VA 22202 Telephone (703) 521-2297

Attachment(s): 1 Certified Copy(ies)

# 日本国特許庁 JAPAN PATENT OFFICE

US

別紙添付の書類に記載されている事項は下記の出願書類に記載されている事項と同一であることを証明する。

This is to certify that the annexed is a true copy of the following application as filed with this Office

出願年月日 Date of Application:

2001年 2月 2日

出願番号 Application Number:

特願2001-027042

出 顧 人 Applicant(s):

日本電気株式会社

CERTIFIED COPY OF PRIORITY DOCUMENT

2001年11月16日

特許庁長官 Commissioner, Japan Patent Office 及川科

出証番号 出証特2001-3101372

## 特2001-027042

【書類名】

特許願

【整理番号】

72310240

【提出日】

平成13年 2月 2日

【あて先】

特許庁長官 殿

【国際特許分類】

G09G

【発明の名称】

液晶表示装置の信号線駆動回路及び信号線駆動方法

【請求項の数】

12

【発明者】

【住所又は居所】

東京都港区芝五丁目7番1号 日本電気株式会社内

【氏名】

小坂 良介

【特許出願人】

【識別番号】

000004237

【氏名又は名称】

日本電気株式会社

【代理人】

【識別番号】

100079164

【弁理士】

【氏名又は名称】

髙橋 勇

【電話番号】

03-3862-6520

【手数料の表示】

【予納台帳番号】 013505

【納付金額】

21,000円

【提出物件の目録】

【物件名】

明細書 1

【物件名】

図面 1

【物件名】

要約書 1

【包括委任状番号】 9003064

【プルーフの要否】

要

【発明の名称】 液晶表示装置の信号線駆動回路及び信号線駆動方法【特許請求の範囲】

【請求項1】 プリチャージ電圧と画像データに応じた階調電圧とを複数の信号線に供給する、液晶表示装置の信号線駆動回路において、

1 水平期間前の前記画像データと次に表示する前記画像データとを前記各信号線ごとに比較する画像データ比較手段と、

この画像データ比較手段での比較結果に応じて前記プリチャージ電圧の供給を 制御するスイッチ制御手段と、

を備えたことを特徴とする液晶表示装置の信号線駆動回路。

【請求項2】 前記スイッチ制御手段は、次に表示する前記画像データの前 記階調電圧が1水平期間前の前記画像データの前記階調電圧の一定範囲内にある 場合に、前記プリチャージ電圧を供給しない、

請求項1記載の液晶表示装置の信号線駆動回路。

【請求項3】 前記スイッチ制御手段は、次に表示する前記画像データの前記階調電圧が1水平期間前の前記画像データの前記階調電圧と一致する場合に、前記プリチャージ電圧を供給しない、

請求項1記載の液晶表示装置の信号線駆動回路。

【請求項4】 前記スイッチ制御手段は、次に表示する前記画像データの前記階調電圧の極性が1水平期間前の前記画像データの前記階調電圧の極性と異なる場合にのみ、前記プリチャージ電圧を供給する、

請求項1記載の液晶表示装置の信号線駆動回路。

【請求項5】 前記スイッチ制御手段は、次に表示する前記画像データの前 記階調電圧の極性が1水平期間前の前記画像データの前記階調電圧の極性と異な る場合に、前記プリチャージ電圧を供給する、

請求項2又は3記載の液晶表示装置の信号線駆動回路。

【請求項6】 前記スイッチ制御手段は、

次に表示する前記画像データの前記階調電圧が1水平期間前の前記画像データ の前記階調電圧よりも大きい場合に、昇圧用に適した第一のオペアンプを用いて 前記階調電圧を供給し、

次に表示する前記画像データの前記階調電圧が1水平期間前の前記画像データの前記階調電圧よりも小さい場合に、降圧用に適した第二のオペアンプを用いて前記階調電圧を供給し、

次に表示する前記画像データの前記階調電圧が1水平期間前の前記画像データ の前記階調電圧と等しい場合に、前記第一及び第二のオペアンプのどちらか一方 を用いて前記階調電圧を供給する、

請求項1乃至5のいずれかに記載の液晶表示装置の信号線駆動回路。

【請求項7】 プリチャージ電圧と画像データに応じた階調電圧とを複数の信号線に供給する、液晶表示装置の信号線駆動方法において、

1 水平期間前の前記画像データと次に表示する前記画像データとを前記各信号 線ごとに比較し、その比較結果に応じて前記プリチャージ電圧の供給を制御する

ことを特徴とする液晶表示装置の信号線駆動方法。

【請求項8】 次に表示する前記画像データの前記階調電圧が1水平期間前の前記画像データの前記階調電圧の一定範囲内にある場合は、前記プリチャージ電圧を供給しない、

請求項7記載の液晶表示装置の信号線駆動方法。

【請求項9】 次に表示する前記画像データの前記階調電圧が1水平期間前の前記画像データの前記階調電圧と一致する場合は、前記プリチャージ電圧を供給しない、

請求項7記載の液晶表示装置の信号線駆動方法。

【請求項10】 次に表示する前記画像データの前記階調電圧の極性が1水平期間前の前記画像データの前記階調電圧の極性と異なる場合にのみ、前記プリチャージ電圧を供給する、

請求項8記載の液晶表示装置の信号線駆動方法。

【請求項11】 次に表示する前記画像データの前記階調電圧の極性が1水平期間前の前記画像データの前記階調電圧の極性と異なる場合は、前記プリチャージ電圧を供給する、

請求項8又は9記載の液晶表示装置の信号線駆動方法。

【請求項12】 次に表示する前記画像データの前記階調電圧が1水平期間前の前記画像データの前記階調電圧よりも大きい場合は、昇圧用に適した第一のオペアンプを用いて前記階調電圧を供給し、

次に表示する前記画像データの前記階調電圧が1水平期間前の前記画像データの前記階調電圧よりも小さい場合は、降圧用に適した第二のオペアンプを用いて前記階調電圧を供給し、

次に表示する前記画像データの前記階調電圧が1水平期間前の前記画像データ の前記階調電圧と等しい場合は、前記第一及び第二のオペアンプのどちらか一方 を用いて前記階調電圧を供給する、

請求項7乃至11のいずれかに記載の液晶表示装置の信号線駆動方法。

## 【発明の詳細な説明】

[0001]

### 【発明の属する技術分野】

本発明は、アクティブマトリクス型などの液晶表示装置に用いられ、低消費電力化に適した、信号線駆動回路及び信号線駆動方法に関する。

[0002]

#### 【従来の技術】

最近の液晶表示装置では、液晶パネルの大型化及び高画質化に伴い、電流駆動能力が高くかつ消費電力の低い駆動回路が求められてきた。そのような要求を満たすものとして、プリチャージ手段を備えた液晶表示装置が知られている(例えば特開平8-87248号公報)。このプリチャージ手段とは、液晶パネル上に配置された画素容量へ階調信号を供給する直前に、所定の基準電位を信号線へ印加するものである。これにより、駆動回路の出力段にかかる負荷を低減することで省電力化を図ることができ、また、負荷のばらつきを抑制することで安定した書き込みが可能となる。

[0003]

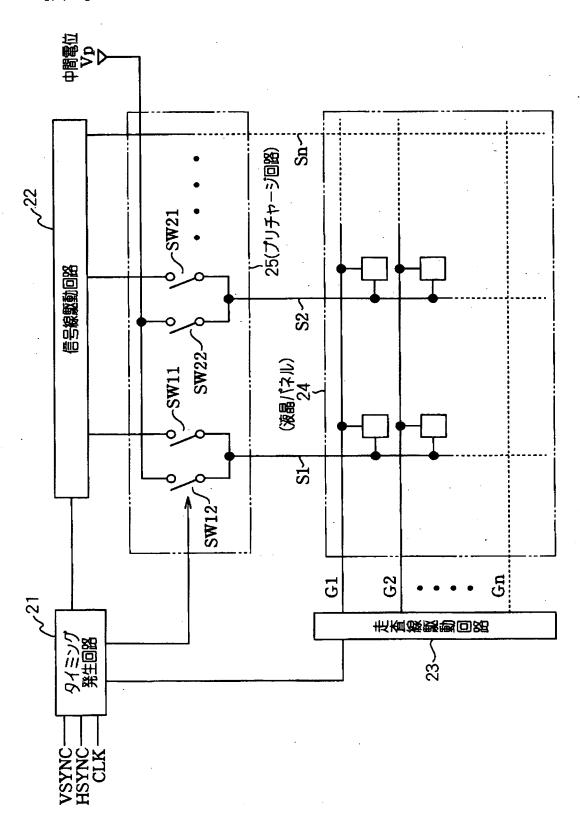

図9は、このようなプリチャージ手段を備えた従来の液晶表示装置を示す回路 図である。以下、この図面に基づき説明する。

## [0004]

プリチャージ回路 2.5 は、信号線 S.1 , S.2 , … , S.n と信号線駆動回路 2.2 の出力側とをそれぞれ接続するスイッチ S.W.1.1 , S.W.2.1 , … , S.W.n.1 、 及び信号線 S.1 , S.2 , … , S.n と中間電位 V.p とをそれぞれ接続するスイッチ S.W.1.2 , S.W.2.2 , … , S.W.n.2 から構成されている。各スイッチ S.W.1.2 , … は、タイミング発生回路 2.1 から供給される信号に基づいて動作する

#### [0005]

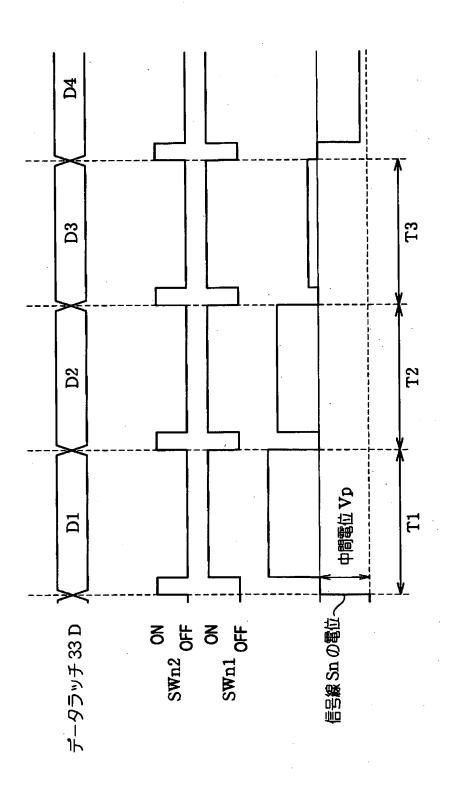

図10は、図9の液晶表示装置における信号線駆動回路の一例を示すブロック 図である。図11は、図10の信号線駆動回路の動作を示すタイミングチャート である。以下、図9乃至図11に基づき説明する。

### [0006]

信号線駆動回路22は、クロック信号CLKにより動作するシフトレジスタ31と、シフトレジスタ31の出力によって制御されmビットの画像データを並列に保持するデータレジスタ32と、制御信号LPにより画像データを一括して転送し保持するデータラッチ33と、mビット入力のデコーダ34と、階調電圧発生回路37から入力する2m個の電圧から階調電圧を選択して出力するアナログスイッチ35と、アナログスイッチ35から出力された階調電圧をプリチャージ回路25へ出力する出力回路36と、前述したプリチャージ回路25とからなる

#### [0007]

スイッチSWn1、SWn2は、それぞれ外部のタイミング発生回路21から 供給されるパルス信号SP1、SP2に従ってオン/オフを切り替える。

#### [0008]

#### 【発明が解決しようとする課題】

従来の信号線駆動回路では、図11の期間T1、T2を参照しても分かるように、1水平期間の前後で供給される階調電圧に関わらず常にプリチャージを行っている。このようなプリチャージは、ドット反転駆動のように異なる極性の階調電圧を供給する場合には非常に有効な手段である。しかしながら、次に表示する

画像データの階調電圧が1水平期間前の画像データの階調電圧と等しい、又はその階調電圧の一定範囲内にある場合、プリチャージを行うことによって信号線の電位変動が大きくなり、その分だけ逆に消費電力量が増加してしまう、という問題があった。

[0009]

ところで、特に携帯電話端末等、各種携帯機器の分野においては、その性質上、液晶パネルの大きさが限定されるため、大型液晶パネルのドライバほどの電流 駆動能力は要求されないが、更なる省電力化が求められている。

[0010]

【発明の目的】

そこで、本発明の目的は、上記の問題点を改善することにより更に消費電力を 低減した、液晶表示装置の信号線駆動回路を提供することにある。

[0011]

【課題を解決するための手段】

本発明に係る信号線駆動回路は、プリチャージ電圧と画像データに応じた階調電圧とを複数の信号線に供給するものであって、1 水平期間前の画像データと次に表示する画像データとを各信号線ごとに比較する画像データ比較手段と、画像データ比較手段での比較結果に応じてプリチャージ電圧の供給を制御するスイッチ制御手段とを備えたことを特徴とする(請求項1)。本発明に係る信号線駆動方法は、本発明に係る信号線駆動回路に使用されるものであって、1 水平期間前の画像データと次に表示する画像データとを各信号線ごとに比較し、その比較結果に応じてプリチャージ電圧の供給を制御することを特徴とする(請求項7)。

[0012]

1 水平期間前に供給された階調電圧と次に供給される階調電圧との変化量が小さい場合は、必ずしもプリチャージが必要ではない。そのような場合にプリチャージを省略することにより、省電力化が図れる。スイッチ制御手段は、例えば次の①~⑤のように動作する。

[0013]

①. 次に表示する画像データの階調電圧が1水平期間前の画像データの階調電

圧の一定範囲内にある場合は、プリチャージ電圧を供給しない(請求項2,8)。「一定範囲内」とは、プリチャージが不要となる範囲のことであり、理論的又は実験的に設定される。

[0014]

②. 次に表示する画像データの階調電圧が1水平期間前の画像データの階調電圧と一致する場合は、プリチャージ電圧を供給しない(請求項3,9)。請求項2,8における「一定範囲内」を限定したものである。

[0015]

③. 次に表示する画像データの階調電圧の極性が1水平期間前の画像データの階調電圧の極性と異なる場合にのみ、プリチャージ電圧を供給する。1水平期間で階調電圧の極性が反転する場合は、階調電圧の変化量が大きい。このような場合にのみプリチャージを実行することにより、省電力化が図れる。

[0016]

④. 次に表示する画像データの階調電圧の極性が1水平期間前の画像データの階調電圧の極性と異なる場合は、プリチャージ電圧を供給する(請求項4,10)。これは請求項2,3,8,9と組み合わせて用いられる。

[0017]

⑤. 次に表示する画像データの階調電圧が1水平期間前の画像データの階調電圧よりも大きい場合は、昇圧用に適した第一のオペアンプを用いて階調電圧を供給し、次に表示する画像データの階調電圧が1水平期間前の画像データの階調電圧よりも小さい場合は、降圧用に適した第二のオペアンプを用いて階調電圧を供給し、次に表示する画像データの階調電圧が1水平期間前の画像データの階調電圧と等しい場合は、第一及び第二のオペアンプのどちらか一方を用いて階調電圧を供給する。他の請求項と組み合わせて用いることにより、更に省電力化が図れる。なお、「昇圧用に適した」とは例えば「昇圧用として省電力化が可能な」という意味であり、「降圧用に適した」とは例えば「降圧用として省電力化が可能な」という意味である。

[0018]

【発明の実施の形態】

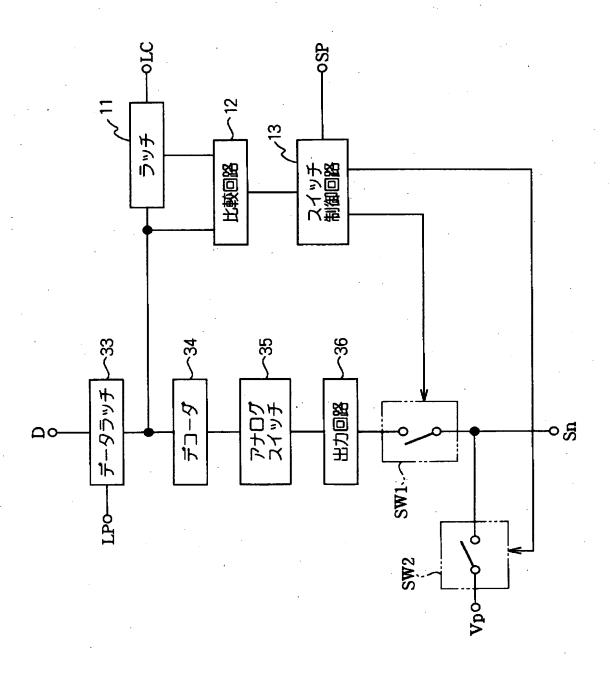

図1は、本発明に係る信号線駆動回路の第一実施形態を示すブロック図である 。以下、この図面に基づき説明する。

### [0019]

本実施形態の信号線駆動回路は、アクティブマトリクス型液晶表示装置に用いられ、プリチャージ電圧としての中間電位Vpと画像データに応じた階調電圧とを複数の信号線に供給するものであり、1水平期間前の画像データと次に表示する画像データとを各信号線ごとに比較する画像データ比較手段としてのラッチ11及び比較回路12と、比較回路12での比較結果に応じて中間電位Vpを供給するスイッチ制御手段としてのスイッチ制御回路13とを備えたことを特徴とする。

### [0020]

また、本実施形態の信号線駆動回路は、図10の従来の信号線駆動回路と同じように、データラッチ33、デコーダ34、アナログスイッチ35、出力回路36、アナログスイッチSW1, SW2等を備えている。なお、本実施形態の信号線駆動回路は、わかりやすくするために、信号線Snのみに対するものとして図示している。したがって、実際には、信号線S1, S2, …, Snのそれぞれに対して本実施形態の信号線駆動回路が設けられる。

#### [0021]

ラッチ11は、データラッチ33の出力側と接続されており、データラッチ33の保持するデータが信号LPによって更新される直前に、データラッチ33から出力されたデータを信号LCに従って取り込む。これにより、ラッチ11は、1水平期間前に表示された画像データを保持することができる。そのため、比較回路12は、データラッチ33の出力信号とラッチ11の出力信号とにより、1水平期間前後の画像データを比較できる。

## [0022]

スイッチ制御回路13は、タイミング発生回路(図9参照)から供給される信号SPと比較回路12の出力信号とに基づいて、アナログスイッチSW1,SW2のオン/オフを切り替える。スイッチSW1がオンすると信号線Snへ出力回路36から階調電圧が供給され、スイッチSW2がオンすると信号線Snへ中間

電位Vpが供給される。

[0023]

このように、本実施形態の信号線駆動回路は、1水平期間前後の画像データの 比較結果に基づいて、信号線Snと中間電位Vpとをショートさせるタイミング すなわちプリチャージを行うタイミングを制御している。したがって、連続した 水平期間で等しい階調信号を供給する場合や、ライン反転駆動のように1フレー ム期間内において供給される階調信号が同一極性であるような場合に、不必要な プリチャージを避けることにより、電力消費を低減することができる。

[0024]

図2は、本発明に係る信号線駆動回路の第二実施形態を示すブロック図である 。以下、この図面に基づき説明する。

[0025]

本実施形態の信号線駆動回路は、第一実施形態を更に具体化したものであり、 1 水平期間前の画像データと次に表示する画像データとを各信号線ごとに比較す る画像データ比較手段としてのラッチ51及び比較回路52と、比較回路52で の比較結果に応じて中間電位Vpを供給するスイッチ制御手段としてのスイッチ 制御回路53とを備えたことを特徴とする。

[0026]

また、本実施形態の信号線駆動回路は、データラッチ43、デコーダ44、アナログスイッチ45、出力アンプ46、アナログスイッチSW1,SW2等を備えている。なお、本実施形態の信号線駆動回路は、わかりやすくするために、信号線Snのみに対するものとして図示している。したがって、実際には、信号線S1,S2,…,Snのそれぞれに対して本実施形態の信号線駆動回路が設けられる。

[0027]

画像データDは、4ビットすなわち16階調である。データラッチ43は、4ビットのラッチ回路であり、信号LPのタイミングに従って画像データDを保持し、取り込んだ画像データDをデコーダ44、ラッチ51及び比較回路52へと転送する。画像データDは、16個の信号の中のいずれかにデコーダ44により

デコードされ、アナログスイッチ45へ出力される。アナログスイッチ45は、デコーダ44から入力した信号に従ってオン/オフを切り替える複数のアナログスイッチ群から構成されており、階調電圧発生回路(図10参照)から入力する電圧V0,…,V16の中から任意の階調電圧を1つ選択し、それを出力する。出力アンプ46は、アナログスイッチ45から入力した階調電圧を、スイッチSW1を介して信号線Snへ供給する。また、信号線SnはスイッチSW2を介して中間電位Vpとも接続される。

### [0028]

1水平期間前の画像データを保持するために設けられたラッチ51は、2ビットのラッチ回路であり、信号LCのタイミングに従ってデータラッチ43から出力される画像データDの上位2ビットを保持し、それを画像データD'として比較回路52へ出力する。ラッチ51は、信号LPによってデータラッチ43の内容が更新される直前にデータを取り込むため、1水平期間前の画像データを保持できる。

### [0029]

比較回路 5 2 は、データラッチ 4 3、ラッチ 5 1 及びスイッチ制御回路 5 3 に接続され、ラッチ 5 1 から供給される 1 水平期間前の画像データ D'と、データラッチ 4 3 から供給される画像データ Dの上位 2 ビットとを受け取り、両者の比較を行う。また、比較回路 5 2 は、画像データ Dの上位 2 ビットと画像データ D'とが一致しているか否かを判別する機能を有する。

#### [0030]

スイッチ制御回路53は、アナログスイッチSW1, SW2の制御端子に接続されており、比較回路52の比較結果信号CMPに基づいてアナログスイッチSW1, SW2のオン/オフを切り替える。アナログスイッチSW1がオンすると、出力アンプ46から出力される任意の階調電圧が信号線Snに供給される。スイッチSW2がオンすると中間電位Vpが信号線Snへ供給されることにより、信号線Snがプリチャージされる。このように、本実施形態の信号線駆動回路は、1水平期間前後の画像データを比較した結果に基づいてアナログスイッチSW2を制御することにより、プリチャージの制御を行う。

## [0031]

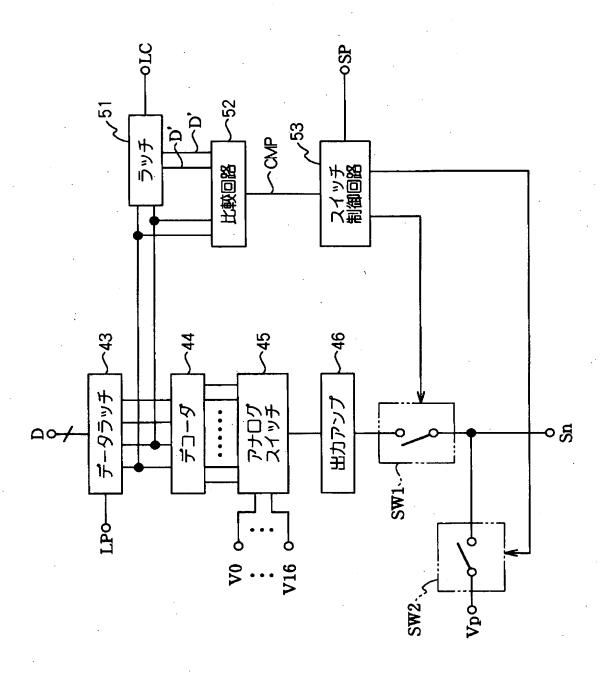

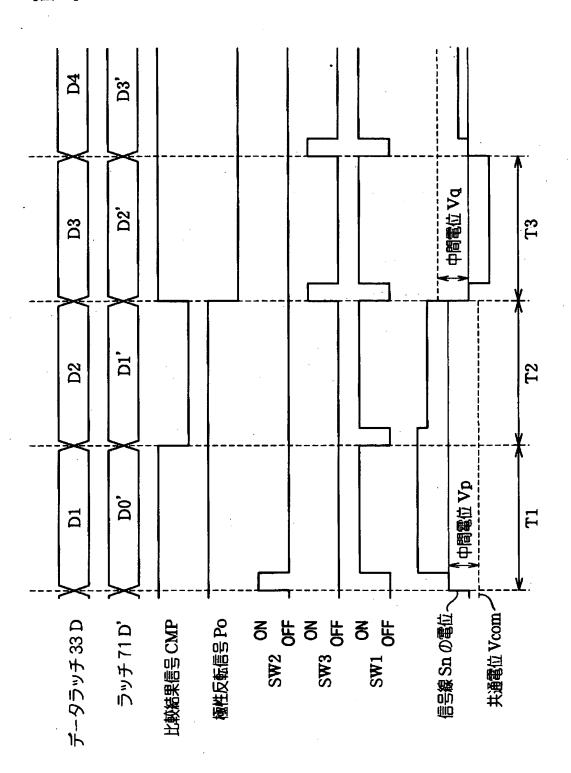

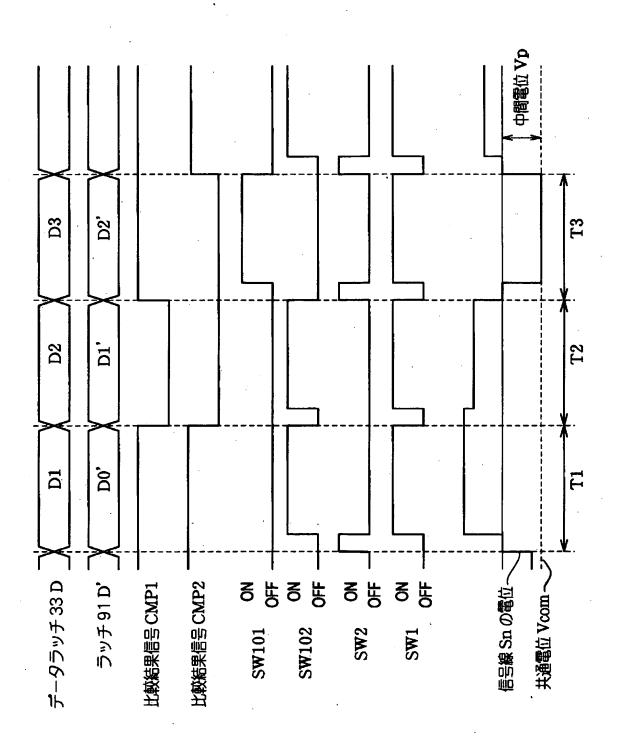

図3は、図2の信号線駆動回路の動作を示すタイミングチャートである。以下、図2及び図3に基づき説明する。

## [0032]

第一の画像データD1が信号線駆動回路に供給されると、画像データD1はデータラッチ43に取り込まれ、デコーダ44へ転送される。デコーダ44及びアナログスイッチ45により、画像データD1に対応する階調電圧がV0,…,V16の中から選択される。選択された階調電圧は、出力アンプ46へ出力され、更にスイッチSW1を介して信号線Snへと供給される。

## [0033]

また、データラッチ43から出力される画像データD1の上位2ビットは、ラッチ51及び比較回路52へも転送される。このとき、ラッチ51の内部には、1水平期間前に表示された画像データの上位2ビットの画像データD0'が保持されている。比較回路52は、2ビットデータの一致回路として構成され、画像データD1の上位2ビットとラッチ51の画像データD0'とを比較し、その比較結果信号CMPをスイッチ制御回路53へ出力する。

#### [0034]

スイッチ制御回路53は、比較の結果が一致しないとき、すなわち、比較結果信号CMP=Hのとき、アナログスイッチSW2をオンさせ、信号線Snを予め設定された中間電位Vpにプリチャージする。続いて、アナログスイッチSW2をオフするのとほぼ同時に、アナログスイッチSW1をオンすることにより、出力アンプ46から出力される階調電圧を信号線Snへ供給する。アナログスイッチSW1,SW2の切替えは、外部のタイミング発生回路から出力される信号SPに基づいて、予め設定されたタイミングで行う(T1)。

#### [0035]

続いて、第二の画像データD2が供給され、データラッチ43が保持するデータが更新される直前に、ラッチ51は信号LCのタイミングに従って画像データD1の上位2ビットを画像データD1'として取り込む。また、画像データD2がデータラッチ43に取り込まれると、上記と同様に、デコーダ44及びアナロ

グスイッチ45を経由して、画像データD2に応じた階調電圧が出力アンプ46 から出力される。

[0036]

同時に、比較回路52は、ラッチ51の画像データD1'と、データラッチ43から出力される画像データD2の上位2ビットとを比較する。これらの二つの画像データが一致する場合、すなわち、画像データD2によって選択される階調電圧と、1水平期間前に供給された画像データD1によって選択された階調電圧との電位差が小さい場合、比較回路52は比較結果信号CMP=Lを出力する。

[0037]

信号線Snの電位変動が小さいと、プリチャージを行わなくても安定した書き込みが可能である。そのため、スイッチ制御回路53は、アナログスイッチSW2をオフしたままプリチャージを行わず、アナログスイッチSW1のみをオンする。アナログスイッチSW1がオンすると、出力アンプ46から出力される階調電圧が信号線Snへ供給される(T2)。

[0038]

同様に、ラッチ51が画像データD2の上位2ビットD2'を取り込み、第三の画像データD3がデータラッチ43へ入力されると、比較回路52はラッチ51の画像データD2'と画像データD3の上位2ビットとを比較する。これらの二つの画像データが一致しないため、比較結果信号CMP=Hとなり、アナログスイッチSW2,SW1が順次オンする。これにより、信号線Snは、中間電位Vpへプリチャージされ、続いて画像データD3に対応した階調電圧が供給される(T3)。

[0039]

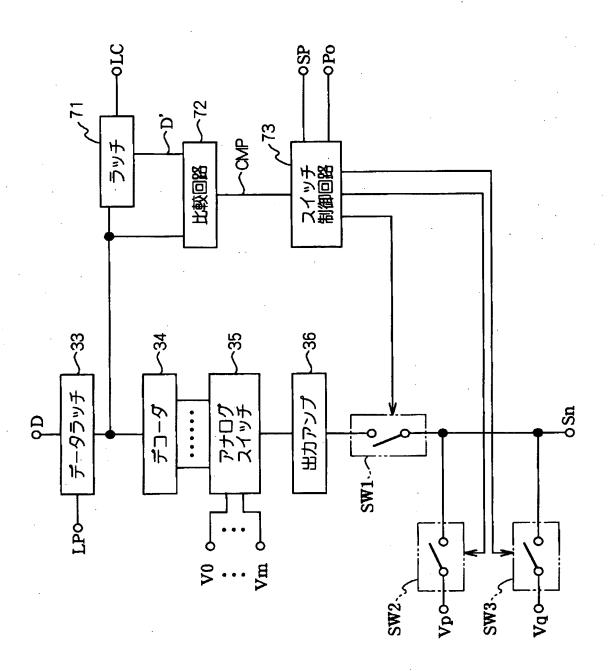

図4は、本発明に係る信号線駆動回路の第三実施形態を示すブロック図である。以下、この図面に基づき説明する。

[0040]

本実施形態の信号線駆動回路は、第一実施形態を交流反転駆動方式へ適用した 具体例であり、1水平期間前の画像データと次に表示する画像データとを各信号 線ごとに比較する画像データ比較手段としてのラッチ71及び比較回路72と、 比較回路72での比較結果に応じて中間電位Vp, Vqを供給するスイッチ制御 手段としてのスイッチ制御回路73とを備えたことを特徴とする。

### [0041]

また、本実施形態の信号線駆動回路は、データラッチ33、デコーダ34、アナログスイッチ35、出力アンプ36、アナログスイッチSW1, SW2, SW3等を備えている。なお、本実施形態の信号線駆動回路は、わかりやすくするために、信号線Snのみに対するものとして図示している。したがって、実際には、信号線S1, S2, …, Snのそれぞれに対して本実施形態の信号線駆動回路が設けられる。

### [0042]

ラッチ71は、nビットのラッチ回路であり、データラッチ33の内容が更新される直前に、データラッチ33から出力される画像データの上位nビット又は全ビットを取り込み、これを保持する。比較回路72は、データラッチ33及びラッチ71から受け取った1水平期間前後の画像データのnビットを比較し、比較結果信号CMPをスイッチ制御回路73へ出力する。スイッチ制御回路73は、比較結果信号CMPと極性反転信号Poとに基づいて、アナログスイッチSW1,SW2,SW3に対し、予め設定されたタイミングでオン/オフを制御する

#### [0043]

信号線Snは、アナログスイッチSW2又はアナログスイッチSW3がオンすることにより中間電位Vp又は中間電位Vaヘプリチャージされる。ただし、中間電位Vpは共通電位Vcomより正極側へ設定され、中間電位Vaは共通電位Vcomより負極側へ設定されている。

#### [0044]

図5は、図4の信号線駆動回路の動作を示すタイミングチャートである。以下 、図4及び図5に基づき説明する。

## [0045]

この極性反転信号Poを用いた信号線駆動回路の動作のタイミングは、図5のようになる。正極側駆動時(Po=H)において、上記第二実施形態と同様に、

比較回路72は第一の画像データD1の上位 n ビットとラッチ71の画像データD0'とを比較する。これらが一致しない場合、スイッチ制御回路73は、アナログスイッチSW2をオンすることにより信号線Snを中間電位Vpにプリチャージし、続いてアナログスイッチSW2をオフし、アナログスイッチSW1をオンすることにより、画像データD1に対応する階調電圧を信号線Snへ供給する(T1)。

### [0046]

第二の画像データD2が供給されると、画像データD2と第一の画像データD1の上位 n ビットとが一致しているため(CMP=L)、プリチャージは行わない。そのため、スイッチ制御回路73は、アナログスイッチSW2をオフのまま、アナログスイッチSW1のみをオンすることにより、信号線Snへ階調電圧を供給する(T2)。

## [0047]

極性反転信号PoがLになると階調電圧が負極性へ反転するため、スイッチ制御回路73は、比較結果信号CMPに関わらずアナログスイッチSW3をオンすることにより、信号線Snを負極側の中間電位Vqにプリチャージする。その後、スイッチ制御回路73は、アナログスイッチSW1をオンすることにより、第三の画像データD3に対応する階調電圧を信号線Snへ供給する(T3)。

## [0048]

同様に、負極側駆動から正極側駆動へ極性反転する場合には、比較の結果に関わらずアナログスイッチSW2をオンすることにより、信号線Snを中間電位Vpへプリチャージする。このように、本実施形態の信号線駆動回路によれば、極性反転駆動を行う場合においてもプリチャージの制御を行うことができるので、低消費電力化が可能となる。

#### [0049]

換言すると、ライン反転駆動方式のように1フレーム期間において液晶パネルに配置された液晶素子へ同極性の電圧を供給する場合、列で隣り合う液晶画素へ書き込む階調信号が等しければ、プリチャージを行わなくとも十分に安定した書き込みが可能である。

[0050]

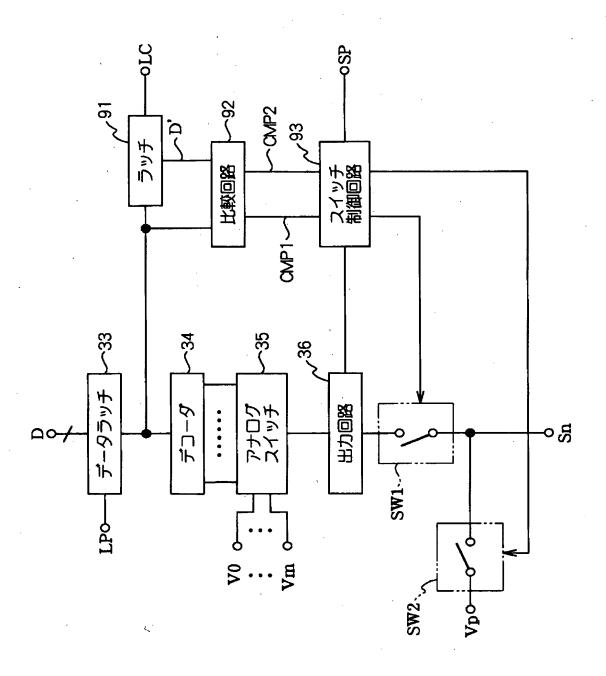

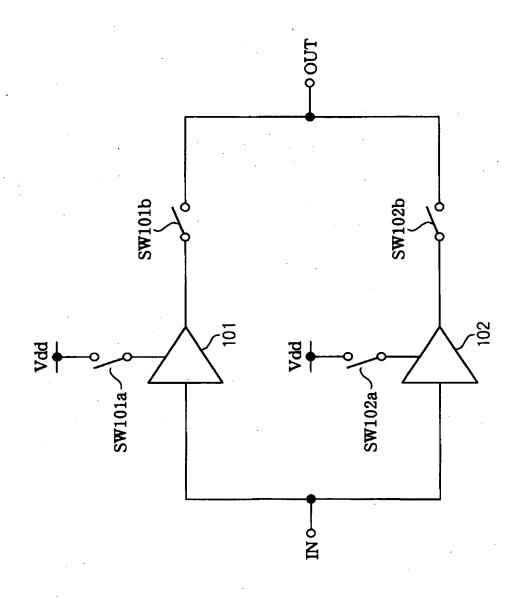

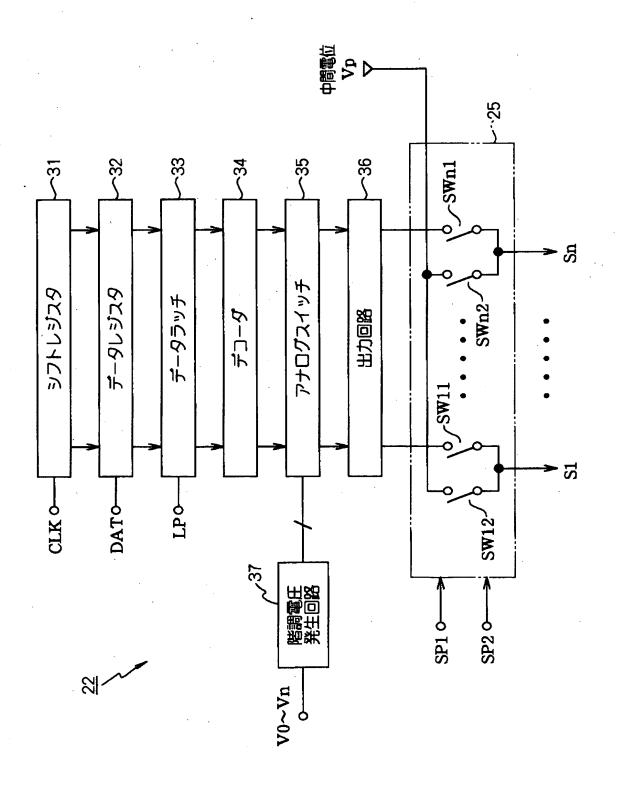

図6は、本発明に係る信号線駆動回路の第四実施形態を示すブロック図である。 図7は、図6の信号線駆動回路における出力回路を示す回路図である。以下、図6及び図7に基づき説明する。

[0051]

本実施形態の信号線駆動回路は、1水平期間前の画像データと次に表示する画像データとを各信号線ごとに比較する画像データ比較手段としてのラッチ91及び比較回路92と、比較回路92での比較結果に応じて中間電位Vpを供給するスイッチ制御手段としてのスイッチ制御回路93とを備えたことを特徴とする。

[0052]

また、本実施形態の信号線駆動回路は、データラッチ33、デコーダ34、アナログスイッチ35、出力回路36、アナログスイッチSW1, SW2等を備えている。なお、本実施形態の信号線駆動回路は、わかりやすくするために、信号線Snのみに対するものとして図示している。したがって、実際には、信号線S1, S2, …, Snのそれぞれに対して本実施形態の信号線駆動回路が設けられる。

[0053]

上記第二及び第三実施形態では、プリチャージを制御する機能を画像データの 上位ビットの一致判定に基づいて実現している。これに対し、本実施形態では、 画像データの大小比較を行う機能を比較回路92に持たせている。

[0054]

出力回路36は、図7に示すように、Nch受けオペアンプ101、Pch受けオペアンプ102、スイッチ群SW101a, SW101b, SW102a, SW102b等から構成される。Nch受けオペアンプ101は主に信号線Snへ電荷を供給するために用いられ、Pch受けオペアンプ102は主に信号線Snの電位を引き下げるために用いられる。

[0055]

ラッチ91は、データラッチ33から出力される画像データDの全ビットを保持できる構成である。比較回路92は、1水平期間前後の画像データの上位1ビ

ットの一致判定を行う機能と、両者の画像データ自体の大きさを比較する機能とを有しており、上位1ビットの比較結果信号をCMP1、大小の比較結果信号をCMP2としてスイッチ制御回路93へ出力する。スイッチ制御回路93は、アナログスイッチSW1,SW2の制御端子、及び図7に示すスイッチSW101a,SW101b,SW102a,SW102bの制御端子へそれぞれ制御信号を出力し、これらのオン/オフを切り替える。

[0056]

図8は、図6の信号線駆動回路の動作を示すタイミングチャートである。以下、図6乃至図8に基づき説明する。

[0057]

図8におけるSW101は図7のSW101a, SW101b、図8におけるSW102は図7のSW102a、SW102bをそれぞれまとめて表したものである。

[0058]

第一の画像データD1がデータラッチ33に取り込まれると、比較回路92は、画像データD1とラッチ91に取り込まれている画像データD0'との上位1ビットの一致判定を行い、比較結果信号CMP1を出力する。これらの二つの画像データが一致しない時(CMP1=H)、スイッチ制御回路93は、スイッチSW2をオンすることにより、信号線Snにプリチャージを行う。

[0059]

また、比較回路92は、画像データD1と画像データD0'との大小比較を行い、比較結果信号CMP2を出力する。CMP2=Hのとき、すなわち、画像データD1に対応する階調電圧が画像データD0'に対応する階調電圧よりも大きいとき、スイッチ制御回路93は、信号線Snがプリチャージされた後、出力回路36のスイッチSW101a, SW101b及びアナログスイッチSW1をオンする。これにより、オペアンプ101は、信号線Snへ電荷をチャージすることにより選択された階調電圧を供給する(T1)。

[0060]

第一の画像データD1がラッチ91に取り込まれ、第二の画像データD2が入

力されると、画像データD1'と画像データD2との上位ビットが一致しているため、比較回路92は比較結果信号CMP1をLとする。すると、アナログスイッチSW2はオフしたままであり、プリチャージは行われない。また、画像データD2は画像データD1'よりも小さい値であるので、比較結果信号CMP2はLとなる。そのため、スイッチ制御回路93は、スイッチSW102a,SW102b及びアナログスイッチSW1をオンすることにより、オペアンプ102を動作させる。すると、信号線Snの電位が引き下げられ、画像データD2に対応する階調電圧が信号線Snに供給される(T2)。

### [0061]

第三の画像データD3が入力されると、ラッチ91の画像データD2'と画像データD3との比較結果によってアナログスイッチSW2がオンとなるので、信号線Snは中間電位Vpにプリチャージされる。続いて、スイッチSW102a、SW102b及びアナログスイッチSW1がオンとなることにより、オペアンプ102は画像データD3に対応する階調電圧を信号線Snへ供給する(T3)

#### [0062]

本実施形態では、1水平期間前後の画像データの上位ビットの比較に基づいてプリチャージを制御するとともに、これらの画像データの大きさを比較することにより二種類のオペアンプを使い分ける構成となっている。通常、出力アンプは立ち上がり速度、立ち下がり速度のギャップを埋めるために、Nch受けオペアンプ及びPch受けオペアンプを組み込んだ構成とすることが多い。また、液晶パネルを動作させるのに十分な駆動能力が要求されるため、オペアンプに流れる定常電流を抑えることは困難である。しかし、本実施形態によれば、画像データを比較することで駆動させるアンプを選択し、使用しないオペアンプに対して電源電圧を供給しないため、出力応答特性を劣化することなく、オペアンプの定常電流を抑えることができることにより、消費電力を更に低減した液晶駆動回路を実現できる。

## [0063]

なお、本発明は、言うまでもなく、上記各実施形態に限定されるものではない

。例えば、上記各実施形態はラッチに取り込んだディジタル画像データを比較する構成となっているが、例えば、コンパレータとサンプルホールド回路とを用いてアナログデータに対して大小比較を行うような構成としてもよい。

[0064]

## 【発明の効果】

本発明に係る信号線駆動回路及び信号線駆動方法によれば、1水平期間前に供給された階調電圧と次に供給される階調電圧との変化量が小さいため、プリチャージがなくても高速かつ安定した書き込みが可能である場合にはプリチャージを行わないことにより、プリチャージに要する電流の損失を低減することができる。したがって、低い消費電力で駆動可能な液晶表示装置を実現することができる

## 【図面の簡単な説明】

【図1】

本発明に係る信号線駆動回路の第一実施形態を示すブロック図である。

【図2】

本発明に係る信号線駆動回路の第二実施形態を示すブロック図である。

【図3】

図2の信号線駆動回路の動作を示すタイミングチャートである。

【図4】

本発明に係る信号線駆動回路の第三実施形態を示すブロック図である。

【図5】

図4の信号線駆動回路の動作を示すタイミングチャートである。

【図6】

本発明に係る信号線駆動回路の第四実施形態を示すブロック図である。

【図7】

図6の信号線駆動回路における出力回路を示す回路図である。

【図8】

図6の信号線駆動回路の動作を示すタイミングチャートである。

【図9】

## 特2001-027042

プリチャージ手段を備えた従来の液晶表示装置を示す回路図である。

## 【図10】

従来の液晶表示装置における信号線駆動回路の一例を示すブロック図である。

## 【図11】

図10の信号線駆動回路の動作を示すタイミングチャートである。

## 【符号の説明】

- 11,51,71,91 ラッチ (画像データ比較手段)

- 12,52,72,92 比較回路(画像データ比較手段)

- 13,53,73,93 スイッチ制御回路(スイッチ制御手段)

- 101, 102 オペアンプ

【書類名】

図面

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

## 特2001-027042

【書類名】

要約書

【要約】

【課題】 プリチャージ手段を備えた液晶表示装置の省電力化を図る。

【解決手段】 本発明の信号線駆動回路は、アクティブマトリクス型液晶表示装置に用いられ、プリチャージ電圧としての中間電位Vpと画像データに応じた階調電圧とを複数の信号線に供給するものであり、1水平期間前の画像データと次に表示する画像データとを各信号線ごとに比較するラッチ11及び比較回路12と、比較回路12での比較結果に応じて中間電位Vpを供給するスイッチ制御回路13とを備えたことを特徴とする。プリチャージがなくても高速かつ安定した書き込みが可能である場合にはプリチャージを行わないため、プリチャージに要する電流の損失を低減することができる。

【選択図】

図 1

# 出願人履歴情報

識別番号

[000004237]

1. 変更年月日 1990年 8月29日

[変更理由] 新規登録

住 所 東京都港区芝五丁目7番1号

氏 名 日本電気株式会社